# **VXIBUS PRODUCTS**

## **DESCRIPTION**

The Model VXI-5524 is a low-cost VXI Interface for connecting virtually any kind of a circuit to the VXIbus. The VXI-5524 is a registerbased VXI interface with enough on-board logic for most applications.

VXI-5524 Interface Board

The VXI-5524 has 48 digital I/O signals to directly control simple circuits or readback data values and a 16-bit VXI data expansion bus for more complex circuitry.

# **Packaging Concept**

The VXI-5524 interface is a narrow PC card that is located at the VXI bus end of the module. The user places his components on a separate printed circuit board which mates with the VXI-5524 to make a complete 'B' or 'C" size assembly. The two cards mate together with a right-angle 96-pin DIN connector and are mechanically held together with a metal bracket.

For quick prototyping, ICS offers a prototype component board with holes on 0.1 inch centers and a bare copper clad board. ICS also supplies design kits and CAD templates so the user can layout his own printed circuit board.

The VXI-5524 can be enclosed with ICS's 11434x series VXI Hardware Kits to make a complete 1, 2, or 3-slot wide module. Each VXI Hardware Kit includes a blank front panel, side shields and all the hardware necessary to make a complete 'C' size Module.

#### User's Interface

The VXI-5524's user interface includes 48 static digital lines, a VXI data expansion bus, TTL trigger lines and VXIbus interrupt lines. The static digital interface has three 16-bit registers that can be used as latched outputs to control the user's circuits or as gated inputs to read back data or signals. The expansion bus is a buffered, 16-bit wide VXI D16

data bus with address capability to read and write to 26 additional registers.

The user interface has a two trigger lines that are connected to a selected pair of the VXIbus TTL Trigger Lines. The input trigger can be used to start an event on the user's circuit. The output trigger line can be used to drive the VXIbus TTL Trigger line and trigger other VXI modules. The user interface has an interrupt line that can be pulsed to generate a VXIbus interrupt on a selected VXI IRQ line. The VXI-5524 reports three user cause code bits as part of the interrupt response word.

The user interface also includes a 10 MHz clock and all seven VXIbus voltages.

# **Easy Configurability**

All of the VXI-5524's configurable functions, such as the manufacturer ID code and model number, serial number, etc. are stored in a nonvolatile E²ROM and are restored when the card is reset or powered on. The user sets the configurable parameters to personalize the finished VXI module as his product.

# **Register Based Interface Advantages**

Data transfer time can limit a module's performance regardless of how good the rest of the circuits are. Message based modules provide the intelligence and flexibility of a on-board processor but are limited by the slow data transfer rate of the VXIbus word serial transfer protocol. VXI-5524 Register based modules are not limited by the word serial protocol as each data register is directly addressable by the VXIbus controller.

#### INTERFACE CARD

# "The fastest way to build a VXI Module"

- Mates with user's PCB to form a C or D-size module. The quickest way to make a VXI module.

- A complete VXI-1 Rev 1.4 and VXI-2 compliant register-based interface. High speed VXIbus interface that meets the latest VXIbus specifications

- User interface includes 48 I/O signals, a VXI expansion bus, TTL Triggers and VXI interrupt capability. Supports virtually any kind of user circuit or function.

- User configureable model number, manufacturer ID, version and serial numbers Identifies the finished module as your product.

- Two companion component boards available for prototype modules

No need to layout prototype boards.

- Companion hardware kits available for building 1, 2 or 3-slot wide modules.

Complete hardware support for all width C-size modules.

7034 Commerce Circle Pleasanton, CA 94588

Phone: 925.416.1000

Fax: 925.416.0105

Web: www.icselect.com

Command interpretation is done in the user's logic or by the device driver in the Bus controller which further speeds up the module's response.

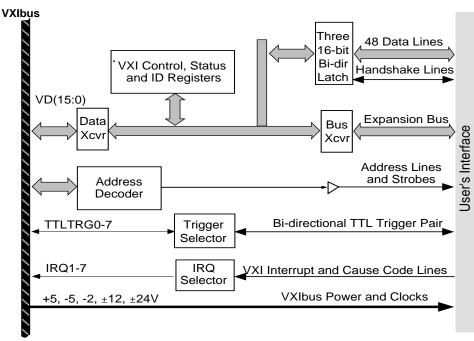

# VXI-5524 Block Diagram

A block diagram of the VXI-5524 is shown in Figure 1 on the right. It shows the 48 bi-directional digital I/O lines, an expansion bus for driving additional circuits, address and strobe lines, VXI triggers, interrupt inputs, power and clocks. This selection of signals makes it very easy for the user to build virtually any kind of a circuit on the mating board. Simple circuits with minimal data needs can be driven directly from the 48 data lines without any additional logic. More complex circuits such as data converters, FIFOs etc. or circuits that need additional I/O lines can be attached to the buffered expansion bus.

#### **Data Lines**

Up to 48 data lines can be controlled by addressing the three bidirectional latches on the VXI-5524. The latch direction is set by bits in the Control Register. When configured as outputs, the latches hold data to drive the user's circuits. The latch outputs are high current drivers capable of sinking 40 mA and sourcing 20 mA. When configured as inputs, the latches operate as CMOS gates to read data from the user's circuits. When more than 48 data lines are needed, additional latches or other circuits can be placed on the user's circuit board and attached to the VXI data expansion bus. The data expansion bus is a 16-bit wide bus that buffers the VXI D16 data lines onto the user's circuit board. Handshake lines include an address select strobe, a write line and a not-ready line to hold the DTACK line.

# **Register Addressing**

All VXI modules are assigned 64 bytes or thirty-two 16-bit word addresses in the A16 address space. The VXI-5524 uses the first sixteen addresses, 00 hex to 1F hex, for its VXI registers and for compliance with the new VXI Specification for Extended Register Based Devices. Addresses 3A-3E hex are used for the 48 data I/O lines. Addresses, 20 hex to 38 hex, are encoded on 4 address lines for

Figure 1 VXI-5524 Block Diagram

the user's logic so they can be easily decoded with a '138' type decoder to address additional devices.

# Trigger and IRQ Lines

The VXI-5524's Trigger Selection logic selects a pair of adjacent VXI TTLTRIG lines and routes them to the user's circuit board. The lower TTLTRG line is an input trigger to initiate action on the user's circuit. The higher TTLTRG line drives a VXIbus TTL Trigger line to trigger other modules.

The VXI-5524's IRQ Selection logic routes a user interrupt onto one of the 7 VXIbus IRQ lines. When the user's logic pulses the IRQ line, the VXI-5524 latches a 3-bit cause code for use in the Interrupt Response word and for the VXI-2 Interrupt Status Register.

#### **Clock and Power**

A clock signal and all VXI voltages are routed to the user's interface connector. A jumper on the VXI-5524 lets the user select the VXI-5524's 10 MHz oscillator or the VXIbus CLK10 signal as the module's clock source.

## **PCB Layout Aids**

ICS provides drawings and CAD design aids to simplify the design of the user's mating PC board to the VXI-5524. The mating board outline drawing and suggested bill of materials are part of the VXI-5524's Instruction Manual.

PCB design files and CAD templates are also available on a CD-ROM. These design aids include the board outline drawings, parts library and a prototype schematic. The CAD files are supplied as DXF files and in ORCAD design format. Both file formats are compatible with most PC layout and schematic capture systems. The prototype schematic includes all of the signals on the user interface. To complete the design, the user just has to add his components to the schematic and route the final design.

Complementary CD-ROMs (Part number 123153) are available at no charge to any qualified VXI designer or customer. Call for your copy or email sales@icselect.com with your name, company name and mailing address.

# TABLE 1 USER INTERFACE SIGNAL-PIN ASSIGNMENTS

# TABLE 2 SIGNAL DEFINITIONS

ated VXIbus trigger on selected TTL

Trigger line.

| USER INTERFACE SIGNAL-PIN ASSIGNMENTS |              |            |              |            |            | SIGNAL DEFINITIONS |                                                                          |

|---------------------------------------|--------------|------------|--------------|------------|------------|--------------------|--------------------------------------------------------------------------|

| Pin                                   | Signal       | Pin        | Signal       | Pin        | Signal     | Signal             | Definition                                                               |

| A1                                    | Inhibit#     | B1         | Cause1       | C1         | + 12 V     | A(1:4)             | Data Bus address lines for VXI regis-                                    |

| A2                                    | Clk10        | В2         | Cause2       | C2         | - 12 V     |                    | ter addresses 20-3A HEX.                                                 |

| A3                                    | NRdy#        | В3         | Cause3/RST#  |            | C3 -2V     | Ass LED#           | Drives Assess LED amuseule beaud                                         |

| A4                                    | Clear#       | B4         | EDR#         | C4         | - 5.2 V    | Acc_LED#           | Drives Access LED onuser's board.                                        |

| A5                                    | Strobe#      | В5         | Vcc          | C5         | Vcc        | Cause1             | User IRQ cause bit 1 (LSB)                                               |

| A6                                    | DWrite#      | В6         | Gnd          | C6         | Gnd        | Cause2             | User IRQ cause bit 2                                                     |

| A7                                    | DStb#        | В7         | D15          | C7         | D7         | Cause3/RST#        | Dual purpose line. If VXI-5524 reset                                     |

| A8                                    | IRQ#         | B8         | D14          | C8         | D6         |                    | jumper is not installed, the line is the                                 |

| A9                                    | TrigOut#     | В9         | D13          | C9         | D5         |                    | User IRQ cause bit 3. If the reset                                       |

| A10                                   | TrigIn#      | B10        | D12          | C10        | D4         |                    | jumper is installed, the line becomes                                    |

| A11                                   | A1           | B11        | D11          | C11        | D3         |                    | a reset input to VXI-5524 board logic.                                   |

| A12                                   | A2           | B12        | D10          | C12        | D2         | CH(1:48)           | Data input-output lines. Data direc-                                     |

| A13                                   | A3           | B13        | D9           | C13        | D1         | C11(1.46)          | tion set in 16 line increments by user                                   |

| A14                                   | A4           | B14        | D8           | C14        | D0         |                    | configuration.                                                           |

| A15                                   | CH48         | B15        | CH40         | C15        | CH32       |                    | O .                                                                      |

| A16                                   | CH47         | B16        | CH39         | C16        | CH31       | Clear#             | Clear strobe to reset user's circuits.                                   |

| A17                                   | CH46         | B17        | CH38         | C17        | CH30       |                    |                                                                          |

| A18                                   | CH45         | B18        | CH37         | C18        | CH29       | Clk10              | 10 MHz clock. VXIbus CLK10 or                                            |

| A19                                   | CH44         | B19        | CH36         | C19        | CH28       |                    | VXI-5524 10 MHZ oscillator.                                              |

| A20                                   | CH43         | B20        | CH35         | C20        | CH27       | D(0:15)            | VXI Expansion Data Bus, D0 is LSB                                        |

| A21                                   | CH42         | B21        | CH34         | C21        | CH26       | D(0.13)            | VAI Expansion Data bus, Do is LSb                                        |

| A22                                   | CH41         | B22        | CH33         | C22<br>C23 | CH25       | DStb#              | Data Bus xfr strobe. Asserted when                                       |

| A23                                   | CH24<br>CH23 | B23<br>B24 | CH16<br>CH15 | C23        | CH8<br>CH7 |                    | Expansion Bus addressed.                                                 |

| A24<br>A25                            | CH23<br>CH22 | B25        | CH13<br>CH14 | C24<br>C25 | CH/<br>CH6 |                    | 1                                                                        |

| A25<br>A26                            | CH22<br>CH21 | B26        | CH14<br>CH13 | C25        | CH6<br>CH5 | DWrite#            | Data Bus in write to user direction.                                     |

| A27                                   | CH20         | B27        | CH12         | C27        | CH4        |                    |                                                                          |

| A28                                   | CH120        | B28        | CH112        | C28        | CH3        | EDR#               | External Data Ready input for hand-                                      |

| A29                                   | CH18         | B29        | CH10         | C29        | CH2        |                    | shaking CH input lines. User sets EDR F/F when data is ready.            |

| A30                                   | CH17         | B30        | CH9          | C30        | CH1        |                    | LDK1/1 when data is ready.                                               |

| A31                                   | Acc_LED#     | B31        | SysFail_LED# | C31        | + 24 V     | Fail_LED           | Drives Failed LED on user's board.                                       |

| A32                                   | Rdy_LED#     | B32        | Fail_LED#    | C32        | - 24 V     | -                  |                                                                          |

|                                       |              |            |              |            |            | Inhibit#           | Inhibit signal from EDR flip-flop. CH inputs should be held steady while |

|                                       |              |            |              |            |            |                    | Inhibit# is asserted.                                                    |

|                                       |              |            |              |            |            | IRQ#               | User generated VXIbus interrupt.                                         |

|                                       |              |            |              |            |            |                    | Latches Cause lines for interrupt re-                                    |

|                                       |              |            |              |            |            |                    | sponse word.                                                             |

|                                       |              |            |              |            |            |                    |                                                                          |

|                                       |              |            |              |            |            | NRdy#              | User generated hold input. Holds                                         |

|                                       |              |            |              |            |            |                    | VXIbus data transfer if NRdy# is low before DataStb# goes high.          |

|                                       |              |            |              |            |            |                    | before Dataston goes fight.                                              |

|                                       |              |            |              |            |            | Rdy_LED#           | Drives Ready LED on user's board.                                        |

|                                       |              |            |              |            |            | Strobe#            | Transfer strobe when CH output data                                      |

|                                       |              |            |              |            |            |                    | is stable.                                                               |

|                                       |              |            |              |            |            | SysFail_LED        | Drives SysFail LED on user's board.                                      |

|                                       |              |            |              |            |            | TrgIn#             | Selected TTL Trigger input line to                                       |

|                                       |              |            |              |            |            |                    | user circuits.                                                           |

|                                       |              |            |              |            |            | TrgOut#            | Trigger output line for user generated VXIbus trigger on selected TTI    |

## **VXI** Specifications

## **VXI** Capabilities

VXI-1 Revision 1.4 compliant VXI-2 Revision 1.0 compliant Static and Dynamic address capability Register based Servant device A16 Address space, D16 Data Programmable interrupter Normal handshake data transfer Includes VXI-2 Version, Serial Number, Interrupt and Subclass Registers.

### Diagnostic Capability

Power-on self test Built-in diagnostic routines Four LEDs for VXI status and troubleshooting.

#### **Indicators**

Four LEDs showing the state of the VX-Ibus interface and VXI-5524's logic.

RDY On after self test

ACCESS On when address recognized

FAIL On when selftest failed SYSFAIL VXIbus SysFail signal line

#### **User Interface**

#### Parallel Data Lines

48 TTL/CMOS latched data lines with 33 Kohm pullups, 20 mA source and 40 mA sink capability. Data line direction set in 16-bit increments. Control lines include input handshake lines and output data strobe. User configuration saved in E²ROM and recalled at power turn-on.

## **Expansion bus**

16 data lines, 4 address lines, strobe and write lines. Expansion bus address range is 20 to 38 HEX. All signals have 20 mA source and 40 mA sink capability.

# **Triggers**

VXI TTLTRG lines selected in pairs.

TTL trigger input pulse. 3 mA source, 20 mA sink capability. Pulse waveform identical to the selected VXIbus TTLTRG line. May be linked to TTLTRG lines 0, 2, 4, or 6.

TTL trigger output line. Drives selected VXI TTLTRG lines 1, 3, 5, or 7.

#### **Interrupter Capability**

Interrupter line and three Cause Code lines. Generates VXIbus interrupt and latches the cause code when the interrupter line is pulsed.

#### Other Signals

CLEAR#: low true pulse to reset user logic. 20 mA source/40 mA sink.

RST#: low true input to reset VXI-5524 logic.

CLK10: VXIbus or VXI-5524 10 MHz clock. 20 mA source/40 mA sink.

LED drive signals for operating four front panel LEDs. 2 mA sink.

# Physical

#### Size, W x H x D

B/C-size narrow card with P1 and P2 VXI bus connectors 9.187in W x 0.62 in H x 3.0 in D (233 mm W x 15.7 mm H x 76.2 mm D)

## Weight

0.14 kg. (0.32 lbs.)

# Power interface logic uses:

5 Vdc @ 300 mA -5.2 Vdc at 45 mA -2 Vdc at 9 mA

#### **User Interface**

A 3 row x 32 pin DIN connector with the signals listed in Table 1.

#### **VXI** Interface

Standard P1 and P2 connectors.

## **Included Accessories**

Instruction manual with PCB layout drawings, design rules for user's PCB and example user circuits.

Programming guide and sample routines for user interface signals, and expansion bus data transfers.

Mounting bracket.

#### **Available Component Boards**

Two boards with mating connector, front panel LEDs and Reset button. Prototyping Board has four power planes and holes on 0.1 inch centers. Bare board has copper-clad on both sides.

#### **Available VXI Kits**

Single, dual and triple wide C-size module hardware kits. Each kit includes side shields, blank front panels and all necessary hardware. Refer to ICS's VXI-KIT data sheet for more information about the 11434x and 114750 hardware kits.

#### ORDERING INFORMATION

Part Number

| VXIbus Register-based Interface Adapter Card with and mounting bracket | VXI-5524                |

|------------------------------------------------------------------------|-------------------------|

| Protoype User Board with holes                                         | 114820                  |

| Prototype User Bare Board (Copper clad)                                | 114830                  |

| VXIbus Hardware Kits                                                   | see separate data sheet |